TPS7A6050EVM

1 Introduction

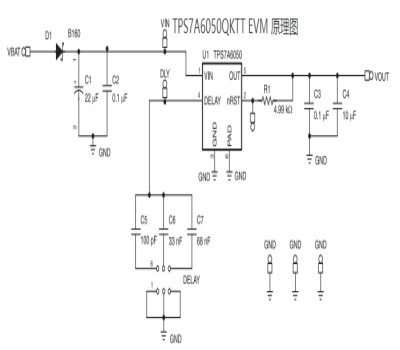

The Texas Instruments TPS7A6050QKTT EVM evaluation module (EVM) helps designers evaluate the operation and performance of the TPS7A6050QKTT Linear Regulator.

2 Setup

This section describes the jumpers and connectors on the EVM as well and how to properly connect, set up and use the TPS7A6050QKTT EVM.

2.1 Input/Output Connector Descriptions

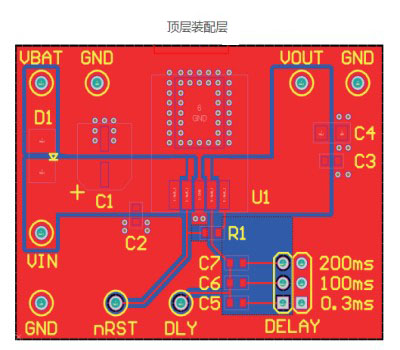

VBAT is the protected power input for the regulator. The test point provides a power (Vbat) connection and a reverse battery protection diode to allow the user to power the EVM.

GND is the ground return for the regulator. The EVM provides three GND test points to allow the user to power the EVM, connect the load and attach an oscilloscope ground lead.

VIN is a power test point. The test point allows the user to measure the input voltage after the reverse battery protection diode. The user can also apply power to the regulator through this test point.

VOUT is power output for the regulator. The test point provides a connection to attach a load to the EVM. DLY is a test point to monitor the charging of the delay capacitor.

nRST is a test point to monitor the reset flag. The reset flag is an active low, open drain output that will remain low when the output voltage is below the power-on reset threshold of approximately 4.65 V.

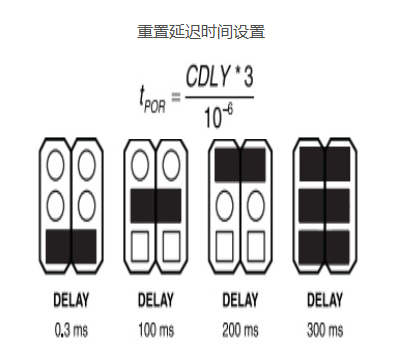

DELAY is the jumper used to set the delay time to hold the nRST pin low after the supply has exceeded the programmed power-on reset threshold voltage of approximately 4.65 V. The jumper capacitors allow the reset delay to be set to four set points. The user can set a specific delay time by changing one of the delay capacitors – C5, C6 or C7. The capacitor value can be set using this equation.

2.2 Setup

The input voltage range for the converter is 5.3 V to 40 V. The EVM can support up to 300 mA of load current.

2.3 Operation

The TPS7A6050QKTT will power-up after the VBAT voltage has exceeded the Power-On Reset threshold. The DELAY jumper should be configured for the desired nRST delay time.

In this configuration, the device will power up when power is applied.

The PCB offers footprints for the TPS7A6050QKTTQ1 or the TPS7A6050QKVUQ1 device.

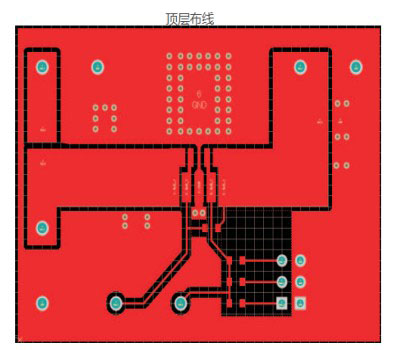

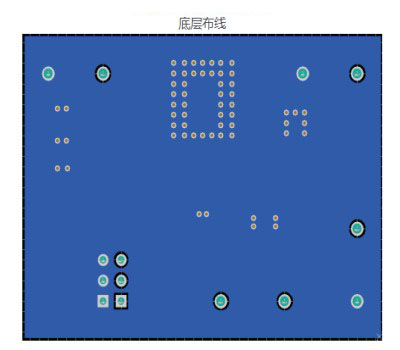

3 Board Layout

Figure 2, Figure 3, and Figure 4 show the board layout for the TPS7A6050QKTT EVM PWB. The EVM offers capacitors and a jumper to program the nRST delay time.

The PowerPAD™ package offers an exposed thermal pad to enhance thermal performance. This must be soldered to the copper landing on the PCB for optimal performance. The PCB provides 2 oz copper planes on the top and bottom to dissipate heat.

4 Schematic and Bill of Materials

- LP8557IEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LAUNCHXL-F28027F TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DLPDLCR160CPEVM DLP160CP TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4631DDAEVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DAC3482EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- THS4302EVM TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7038Q1EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- LM3450AEV230V30/NOPB_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TPS72728DSEEVM-406_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- WL1835MODCOM8A_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TAS5424BQ1DKDEVM_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- ADS7042EVM-PDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- TMDS570LS31HDK_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- VCA8500BOARD_TI(德州仪器)中文资料_英文资料_价格_PDF手册

- DEM-SOT223LDO_TI(德州仪器)中文资料_英文资料_价格_PDF手册